- Core Configuration:核配置选项,配置以太网功能模块,是否包含PCS模块、FIFO模块,配置接口类型、端口数等;

- MAC Options:MAC配置选项,配置MAC模块功能;

- FIFO Options:FIFO存储器选项,可设置FlFO存储器类型以及存储器数据长度;

- PCS/SGMII Options:物理介质接入层模块配置页面,配置物理层。

-

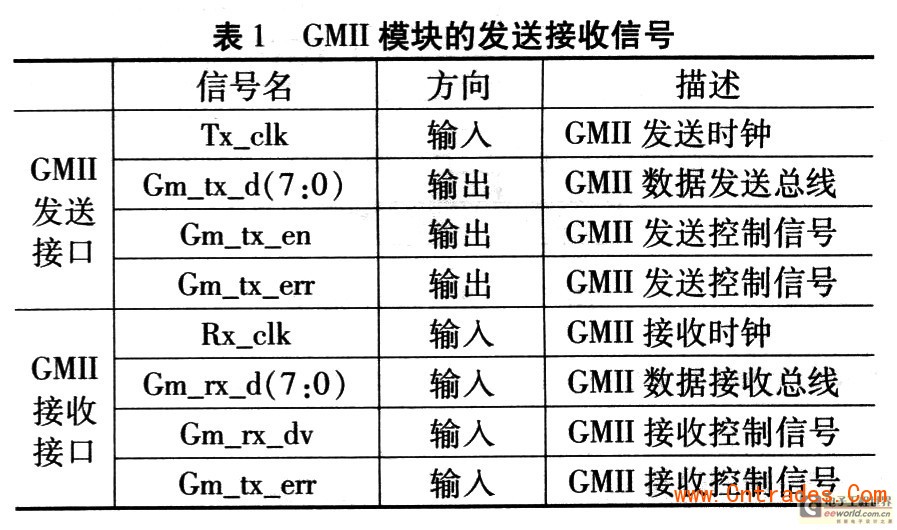

相应的接口信号包括:控制接口信号,复位信号,MAC系统端信号(包括接收接口信号和发送接口信号),MAC以太网端信号(包括GMII模块信号和PHY管理接口信号)。

表1中描述了MAC以太网端GMII模块信号、接口信号,其余信号参考千兆以太网用户手册。GMII模块的接收信号一般直接连到PHY器件,负责与PHY器件的数据交互,其信号与PHY器件接口一一对应,如表1所列。

4 物理层(PHY)器件

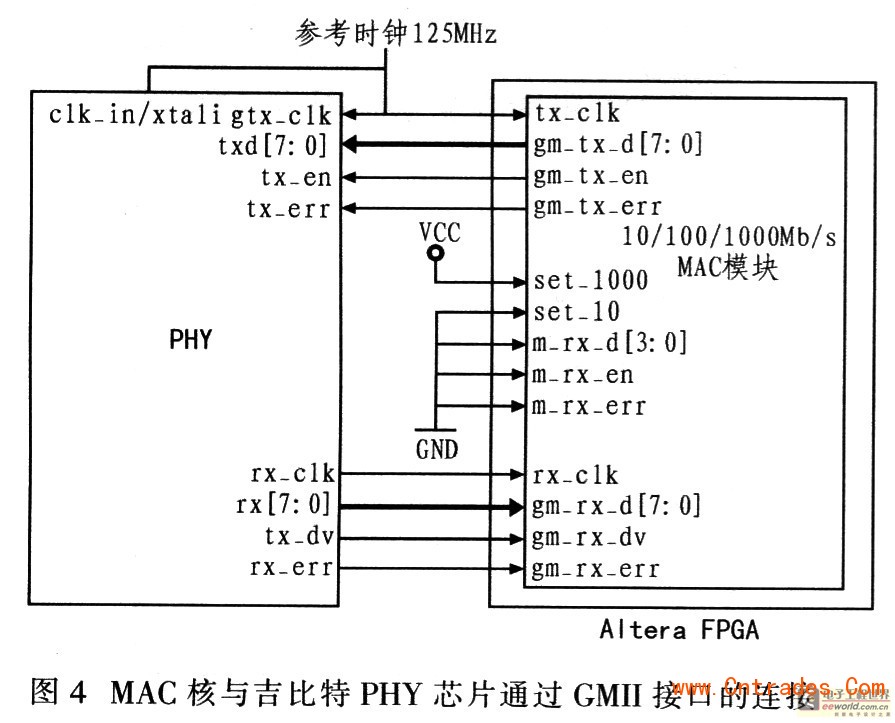

Ahera公司的千兆以太网MAC核默认支持的物理层器件有支持10/100 Mb/s的National DP83848C,支持10/100/1 000 Mb/s的National DP83865,Marveil 88E1145以及支持双物理层和10/100/l 000 Mb/s的Marvell 88E1111。在此,选择National DP83865为PHY器件。

MAC核与吉比特PHY器件通过GMII接口的连接如图4所示。

2022年-中铁二十局集团有限公司雄商高铁站前七标项目经理部

2022年-中铁二十局集团有限公司雄商高铁站前七标项目经理部 2022年-陕西延长石油延安能源化工有限责任公司聚烯烃灌装

2022年-陕西延长石油延安能源化工有限责任公司聚烯烃灌装 2022年-麻家梁煤业有限责任公司工作面奥灰水地面区域治理

2022年-麻家梁煤业有限责任公司工作面奥灰水地面区域治理 2022年-亚洲基础设施投资银行贷款河南郑州等地特大暴

2022年-亚洲基础设施投资银行贷款河南郑州等地特大暴

华润电力红安天明150MW风电项目220kV升压站PC工程

华润电力红安天明150MW风电项目220kV升压站PC工程 华润清远清新林泉扩建50MW风电项目主体施工工程招标公告

华润清远清新林泉扩建50MW风电项目主体施工工程招标公告 华润水泥合浦分布式光伏项目EPC工程总承包招标公告

华润水泥合浦分布式光伏项目EPC工程总承包招标公告 华润电力鲤鱼江电厂贮灰场环境治理及综合利用光伏项目110kV

华润电力鲤鱼江电厂贮灰场环境治理及综合利用光伏项目110kV 山西阳泉矿区泊里煤矿项目井底车场水仓、主排水泵房及主变电所掘

山西阳泉矿区泊里煤矿项目井底车场水仓、主排水泵房及主变电所掘 山西乡宁焦煤集团东沟煤业有限公司工业广场边坡项目治理工程总

山西乡宁焦煤集团东沟煤业有限公司工业广场边坡项目治理工程总 利用亚行贷款中国—东盟中小企业协同创新发展综合提升

利用亚行贷款中国—东盟中小企业协同创新发展综合提升 中铁二十局集团有限公司雄商高铁站前七标项目经理部粉煤灰

中铁二十局集团有限公司雄商高铁站前七标项目经理部粉煤灰 陕西延长石油延安能源化工有限责任公司聚烯烃灌装改造

陕西延长石油延安能源化工有限责任公司聚烯烃灌装改造 麻家梁煤业有限责任公司工作面奥灰水地面区域治理工程招标公告

麻家梁煤业有限责任公司工作面奥灰水地面区域治理工程招标公告 亚洲基础设施投资银行贷款河南郑州等地特大暴雨洪涝灾害灾后恢复

亚洲基础设施投资银行贷款河南郑州等地特大暴雨洪涝灾害灾后恢复 (2022年)鲁山豫能抽水蓄能有限公司河南鲁山抽水蓄能电站安

(2022年)鲁山豫能抽水蓄能有限公司河南鲁山抽水蓄能电站安 (2022年)海南新媒体绿都一期项目(西地块)电梯采购与安装

(2022年)海南新媒体绿都一期项目(西地块)电梯采购与安装 (2022年)同煤大唐塔山煤矿有限公司四盘区立井井筒装备安装

(2022年)同煤大唐塔山煤矿有限公司四盘区立井井筒装备安装 (2022年)亚洲开发银行贷款山西城乡水源保护和环境改善示范

(2022年)亚洲开发银行贷款山西城乡水源保护和环境改善示范 2022年-首钢股份公司迁安钢铁公司炼铁作业部烧结精

2022年-首钢股份公司迁安钢铁公司炼铁作业部烧结精 2022年-江苏省液化天然气储运调峰工程项目取排水工程施工

2022年-江苏省液化天然气储运调峰工程项目取排水工程施工 2022年-山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合

2022年-山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合 2022年-山西忻州神达原宁煤业有限公司90万吨/年矿井兼并

2022年-山西忻州神达原宁煤业有限公司90万吨/年矿井兼并 2022年-成庄矿选煤厂煤泥干燥系统改造工程招标公告

2022年-成庄矿选煤厂煤泥干燥系统改造工程招标公告 2022年-高青县春汇综合智能仓配物流园项目施工总承包

2022年-高青县春汇综合智能仓配物流园项目施工总承包 2022年-陕西中烟工业有限责任公司汉中卷烟厂卷包除尘

2022年-陕西中烟工业有限责任公司汉中卷烟厂卷包除尘 2022年-同煤大唐塔山煤矿有限公司煤泥烘干生产线清洁热源工

2022年-同煤大唐塔山煤矿有限公司煤泥烘干生产线清洁热源工 2022年-承德航天天启风光储氢一体化多能互补示范项目

2022年-承德航天天启风光储氢一体化多能互补示范项目 2022年-利用亚洲开发银行贷款农业综合开发长江绿色生态廊道

2022年-利用亚洲开发银行贷款农业综合开发长江绿色生态廊道 2022年-嵩县前河矿业有限责任公司葚沟矿区天井钻机工程

2022年-嵩县前河矿业有限责任公司葚沟矿区天井钻机工程 2022年-广东陆河抽水蓄能电站施工电源工程建设项目招标公告

2022年-广东陆河抽水蓄能电站施工电源工程建设项目招标公告 首钢股份公司迁安钢铁公司炼铁作业部烧结精3、返8通廊加固设计

首钢股份公司迁安钢铁公司炼铁作业部烧结精3、返8通廊加固设计 江苏省液化天然气储运调峰工程项目取排水工程施工招标公告

江苏省液化天然气储运调峰工程项目取排水工程施工招标公告 山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合项目矿建工程

山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合项目矿建工程 山西忻州神达原宁煤业有限公司90万吨/年矿井兼并重组整合项目

山西忻州神达原宁煤业有限公司90万吨/年矿井兼并重组整合项目 高速公路上交通指示牌

高速公路上交通指示牌 西安恒力仪表SIGRID智能矢量变频电动执行器进口执行器替换

西安恒力仪表SIGRID智能矢量变频电动执行器进口执行器替换 斩拌机视频,125斩拌机视频,斩拌机切肉视频

斩拌机视频,125斩拌机视频,斩拌机切肉视频 回收微晶蜡

回收微晶蜡 多易拍华中区办事处广告宣传片

多易拍华中区办事处广告宣传片 煤炭化验设备

煤炭化验设备 东莞贝朗机械不锈钢线材折弯机设备魅力无限招人羡

东莞贝朗机械不锈钢线材折弯机设备魅力无限招人羡 三维动画、创意动画、影视动画广告

三维动画、创意动画、影视动画广告 五金模具产品

五金模具产品 质量最好粘钢胶厂家

质量最好粘钢胶厂家 公司形象

公司形象 304不锈钢卫浴管

304不锈钢卫浴管 双面单立柱

双面单立柱 深圳艾迪亚设计

深圳艾迪亚设计 异形卡,钥匙扣,IC卡,智能卡,匙扣卡,VIP卡,贵宾卡

异形卡,钥匙扣,IC卡,智能卡,匙扣卡,VIP卡,贵宾卡 酒店沙发

酒店沙发 青海省黄南州泽库县回收废旧化工原料13932031675

青海省黄南州泽库县回收废旧化工原料13932031675 北京收购MOS管

北京收购MOS管 闸北区徐汇一卡通回收

闸北区徐汇一卡通回收 金盐什么检测含量》

金盐什么检测含量》 上门回收家具漆阜宁价格

上门回收家具漆阜宁价格 北京电子产品回收价格北京二手电脑回收公司

北京电子产品回收价格北京二手电脑回收公司 港闸区大型发电机组出租18513089999(收购价格)

港闸区大型发电机组出租18513089999(收购价格) 《泰兴二手配电柜回收》+$铜板铜牌母线槽回收利用

《泰兴二手配电柜回收》+$铜板铜牌母线槽回收利用 呼和浩特大量废旧电缆回收 呼和浩特回收二手电缆18849275178

呼和浩特大量废旧电缆回收 呼和浩特回收二手电缆18849275178 江门恩平二手格力中央空调回收

江门恩平二手格力中央空调回收 全球与中国绿色果汁市场竞争现状与发展潜力分析报告2019年版

全球与中国绿色果汁市场竞争现状与发展潜力分析报告2019年版 无锡市潜水打捞队欢迎咨询

无锡市潜水打捞队欢迎咨询 诸城发电机出租、、租赁《惊喜》18663521519【长期有效】

诸城发电机出租、、租赁《惊喜》18663521519【长期有效】 河池自来水消毒设备供水补给

河池自来水消毒设备供水补给 遵义防腐木河边地板围栏厂18585095799

遵义防腐木河边地板围栏厂18585095799 QP980宝钢

QP980宝钢