RC6是作为AES(Advanced Encryption Standard)的候选算法提交给NIST(美国国家标准局)的一种新的分组密码。它是在RC5的基础上设计的,以更好地符合AES的要求,且提高了安全性,增强了性能。根据AES的要求,一个分组密码必须处理128位输入/输出数据。尽管RC5是一个非常快的分组密码,但它处理128位分组块时用了2个64位工作寄存器;而AES目前在讲究效率和简洁方面不支持64位操作,于是RC6修正这个错误,使用4个32位寄存器而不是2个64位寄存器,以更好地实现加解密。利用FPGA来实现RC6算法,可以提高运算速度。芯片设计为RC6算法处理器,辅助计算机处理器完成加解密操作,可以方便地实现对加解密的分析和研究。因此,此芯片可以作为协处理器来看待。

1 RC6算法

1.1 RC6算法概述

RC6秉承了RC5设计简单、广泛使用数据相关的循环移位思想,同时增强了抵抗攻击的能力,改进了RC5中循环移位的位数不依赖于寄存器中所有位的不足。RC6新的特色是输入的明文由原先2个区块扩展为4个,另外在运算方面则是使用了整数乘法,而整数乘法的使用则在每一个运算回合中增加了扩散(diffusion)的行为,并且使得即使很少的回合数也有很高的安全性。同时,RC6中所用的操作可以在大部分处理器上高效率地实现,提高了加密速度。RC6是一种安全、架构完整而且简单的区块加密法。它提供了较好的测试结果和参数方面相当大的弹性。RC6可以抵抗所有已知的攻击,能够提供AES所要求的安全性,可以说是近几年来相当优秀的一种加密法。

RC6不再使用2个64位工作寄存器,而是用4个32位寄存器。这就使得在每次循环中要进行2次循环移位操作,让更多的数据位来决定循环次数。RC6把明文分别存在4个区块A、B、C、D,刚开始分别包含明文的初始值,加密运算后则为4个密文的输出值。

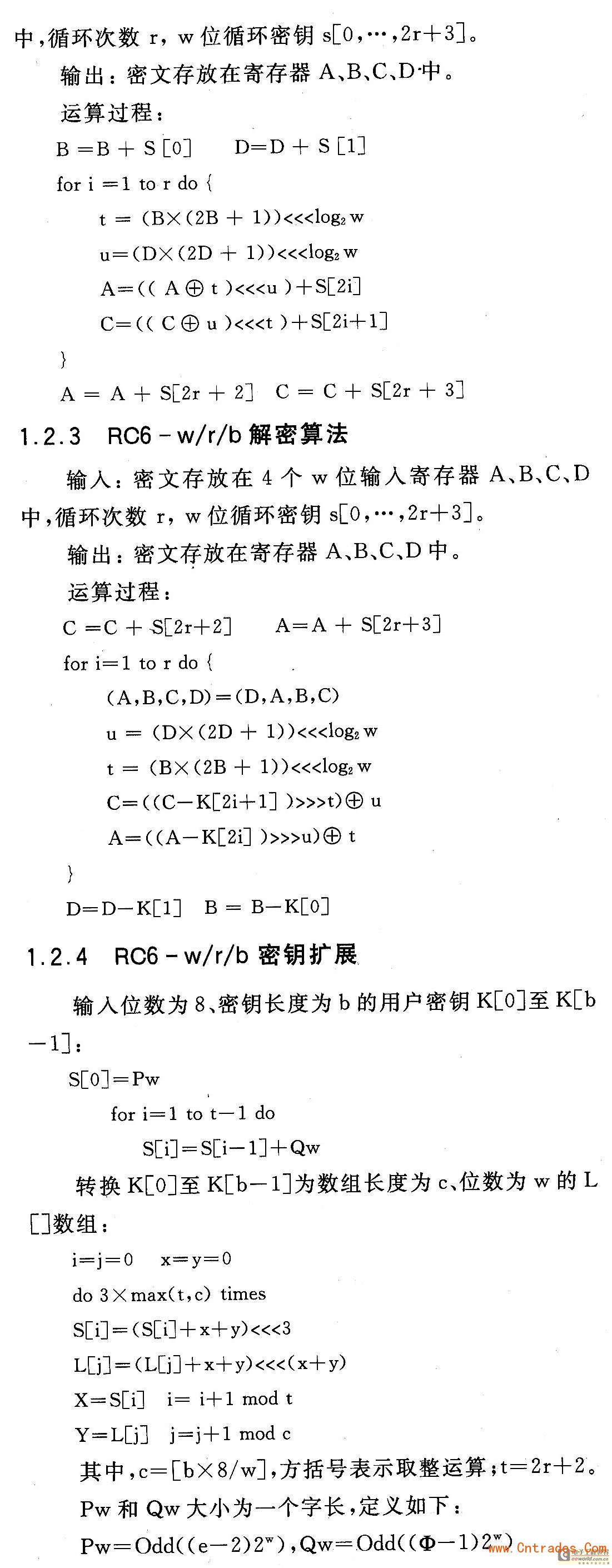

1.2 RC6的工作原理

RC6是参数变量的分组算法,实际上是由3个参数确定的一个加密算法族。一个特定的RC6可以表示为RC6一w/r/b,3个参数w、r和b分别为字长、循环次数和密钥长度。AES中,w=32,r=20。本设计中,密钥长度b为128位(16字节)。RC6用4个w位的寄存器A、B、C、D来存放输入的明文和输出的密文。明文和密文的**个字节存放在A的**字节,经过加解密后,得到的明文和密文的**后一个字节存放在D的**高字节。

1.2.1 RC6一w/r/b基本运算

基本运算共有如下6种:①模2w加算运算,表示为“+”;②模2w减法运算,表示为“一”;③逐位异或运算,表示为“?”;④循环左移,字a循环左移b位表示为“a<<>>b”;⑥模2w乘法,表示为“×”。

1.2.2 RC6一w/r/b加密算法

输入:明文存放在4个w位输入寄存器A、B、C、D

2022年-中铁二十局集团有限公司雄商高铁站前七标项目经理部

2022年-中铁二十局集团有限公司雄商高铁站前七标项目经理部 2022年-陕西延长石油延安能源化工有限责任公司聚烯烃灌装

2022年-陕西延长石油延安能源化工有限责任公司聚烯烃灌装 2022年-麻家梁煤业有限责任公司工作面奥灰水地面区域治理

2022年-麻家梁煤业有限责任公司工作面奥灰水地面区域治理 2022年-亚洲基础设施投资银行贷款河南郑州等地特大暴

2022年-亚洲基础设施投资银行贷款河南郑州等地特大暴

华润电力红安天明150MW风电项目220kV升压站PC工程

华润电力红安天明150MW风电项目220kV升压站PC工程 华润清远清新林泉扩建50MW风电项目主体施工工程招标公告

华润清远清新林泉扩建50MW风电项目主体施工工程招标公告 华润水泥合浦分布式光伏项目EPC工程总承包招标公告

华润水泥合浦分布式光伏项目EPC工程总承包招标公告 华润电力鲤鱼江电厂贮灰场环境治理及综合利用光伏项目110kV

华润电力鲤鱼江电厂贮灰场环境治理及综合利用光伏项目110kV 山西阳泉矿区泊里煤矿项目井底车场水仓、主排水泵房及主变电所掘

山西阳泉矿区泊里煤矿项目井底车场水仓、主排水泵房及主变电所掘 山西乡宁焦煤集团东沟煤业有限公司工业广场边坡项目治理工程总

山西乡宁焦煤集团东沟煤业有限公司工业广场边坡项目治理工程总 利用亚行贷款中国—东盟中小企业协同创新发展综合提升

利用亚行贷款中国—东盟中小企业协同创新发展综合提升 中铁二十局集团有限公司雄商高铁站前七标项目经理部粉煤灰

中铁二十局集团有限公司雄商高铁站前七标项目经理部粉煤灰 陕西延长石油延安能源化工有限责任公司聚烯烃灌装改造

陕西延长石油延安能源化工有限责任公司聚烯烃灌装改造 麻家梁煤业有限责任公司工作面奥灰水地面区域治理工程招标公告

麻家梁煤业有限责任公司工作面奥灰水地面区域治理工程招标公告 亚洲基础设施投资银行贷款河南郑州等地特大暴雨洪涝灾害灾后恢复

亚洲基础设施投资银行贷款河南郑州等地特大暴雨洪涝灾害灾后恢复 (2022年)鲁山豫能抽水蓄能有限公司河南鲁山抽水蓄能电站安

(2022年)鲁山豫能抽水蓄能有限公司河南鲁山抽水蓄能电站安 (2022年)海南新媒体绿都一期项目(西地块)电梯采购与安装

(2022年)海南新媒体绿都一期项目(西地块)电梯采购与安装 (2022年)同煤大唐塔山煤矿有限公司四盘区立井井筒装备安装

(2022年)同煤大唐塔山煤矿有限公司四盘区立井井筒装备安装 (2022年)亚洲开发银行贷款山西城乡水源保护和环境改善示范

(2022年)亚洲开发银行贷款山西城乡水源保护和环境改善示范 2022年-首钢股份公司迁安钢铁公司炼铁作业部烧结精

2022年-首钢股份公司迁安钢铁公司炼铁作业部烧结精 2022年-江苏省液化天然气储运调峰工程项目取排水工程施工

2022年-江苏省液化天然气储运调峰工程项目取排水工程施工 2022年-山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合

2022年-山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合 2022年-山西忻州神达原宁煤业有限公司90万吨/年矿井兼并

2022年-山西忻州神达原宁煤业有限公司90万吨/年矿井兼并 2022年-成庄矿选煤厂煤泥干燥系统改造工程招标公告

2022年-成庄矿选煤厂煤泥干燥系统改造工程招标公告 2022年-高青县春汇综合智能仓配物流园项目施工总承包

2022年-高青县春汇综合智能仓配物流园项目施工总承包 2022年-陕西中烟工业有限责任公司汉中卷烟厂卷包除尘

2022年-陕西中烟工业有限责任公司汉中卷烟厂卷包除尘 2022年-同煤大唐塔山煤矿有限公司煤泥烘干生产线清洁热源工

2022年-同煤大唐塔山煤矿有限公司煤泥烘干生产线清洁热源工 2022年-承德航天天启风光储氢一体化多能互补示范项目

2022年-承德航天天启风光储氢一体化多能互补示范项目 2022年-利用亚洲开发银行贷款农业综合开发长江绿色生态廊道

2022年-利用亚洲开发银行贷款农业综合开发长江绿色生态廊道 2022年-嵩县前河矿业有限责任公司葚沟矿区天井钻机工程

2022年-嵩县前河矿业有限责任公司葚沟矿区天井钻机工程 2022年-广东陆河抽水蓄能电站施工电源工程建设项目招标公告

2022年-广东陆河抽水蓄能电站施工电源工程建设项目招标公告 首钢股份公司迁安钢铁公司炼铁作业部烧结精3、返8通廊加固设计

首钢股份公司迁安钢铁公司炼铁作业部烧结精3、返8通廊加固设计 江苏省液化天然气储运调峰工程项目取排水工程施工招标公告

江苏省液化天然气储运调峰工程项目取排水工程施工招标公告 山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合项目矿建工程

山西忻州神达万鑫安平煤业有限公司矿井兼并重组整合项目矿建工程 山西忻州神达原宁煤业有限公司90万吨/年矿井兼并重组整合项目

山西忻州神达原宁煤业有限公司90万吨/年矿井兼并重组整合项目 富翔金属电子塑料回收有限公司

富翔金属电子塑料回收有限公司 岳阳C8车载泵楼面施工视频

岳阳C8车载泵楼面施工视频 【VIP】北京到乌鲁木齐轿车托运公司至多少钱

【VIP】北京到乌鲁木齐轿车托运公司至多少钱 二手1T叉车价格_二手合力1T叉车出售_二手杭叉1T叉车报价

二手1T叉车价格_二手合力1T叉车出售_二手杭叉1T叉车报价 帕旗HDMI机顶盒共享器无线高清系列PAKITE视频介绍指导

帕旗HDMI机顶盒共享器无线高清系列PAKITE视频介绍指导 深圳丰韬广告 LED发光字 深圳led发光字

深圳丰韬广告 LED发光字 深圳led发光字 小口径无缝钢管精密无缝钢管山东无缝钢管大量供应

小口径无缝钢管精密无缝钢管山东无缝钢管大量供应 ECMT-104C全自动化妆海绵平切机

ECMT-104C全自动化妆海绵平切机 浦江明新水晶影像耗材厂

浦江明新水晶影像耗材厂 公司资质

公司资质 成品库房

成品库房 深州市瑞峰机械配件厂

深州市瑞峰机械配件厂 上海烨直管道科技有限公司

上海烨直管道科技有限公司 沈阳庆典活动道具供应商

沈阳庆典活动道具供应商 牡丹江声测管厂家

牡丹江声测管厂家 户外全彩LED显示屏系列

户外全彩LED显示屏系列 宿州车床回收(旧车床)13521292070

宿州车床回收(旧车床)13521292070 甘孜数控车床回收为您服务 数控机床回收整场机械 旧机床回收

甘孜数控车床回收为您服务 数控机床回收整场机械 旧机床回收 东莞电线电缆回收

东莞电线电缆回收 广州海珠区大金中央空调回收中心

广州海珠区大金中央空调回收中心 淮北收购爱特梅尔Atmell芯片收购单片机

淮北收购爱特梅尔Atmell芯片收购单片机 广东回收价格光猫F607_光猫F607中兴板卡长期收购

广东回收价格光猫F607_光猫F607中兴板卡长期收购 广州市荔湾区废品回收公司废旧马达回收价格

广州市荔湾区废品回收公司废旧马达回收价格 回收二手食品级储液罐

回收二手食品级储液罐 枣庄最有名刑事辩护律师枣庄市律师事务所

枣庄最有名刑事辩护律师枣庄市律师事务所 西安防火防爆柜厂家电话

西安防火防爆柜厂家电话 企业备案标准

企业备案标准 清河潜水作业公司欢迎您

清河潜水作业公司欢迎您 广州至威海货运→精品专线

广州至威海货运→精品专线 梅州长途救护车转运120救护车收费价格

梅州长途救护车转运120救护车收费价格 东营欧米茄二手官网|旧表回收

东营欧米茄二手官网|旧表回收 上海青浦斯达克Halo爱风2二代爱风助听器多少钱

上海青浦斯达克Halo爱风2二代爱风助听器多少钱